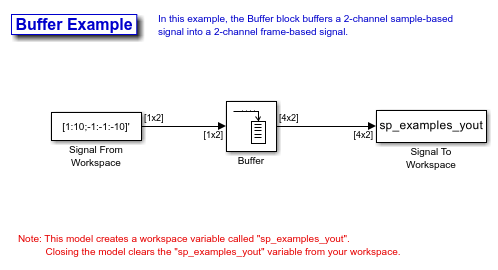

Buffering and Frame-Based Processing - MATLAB & Simulink

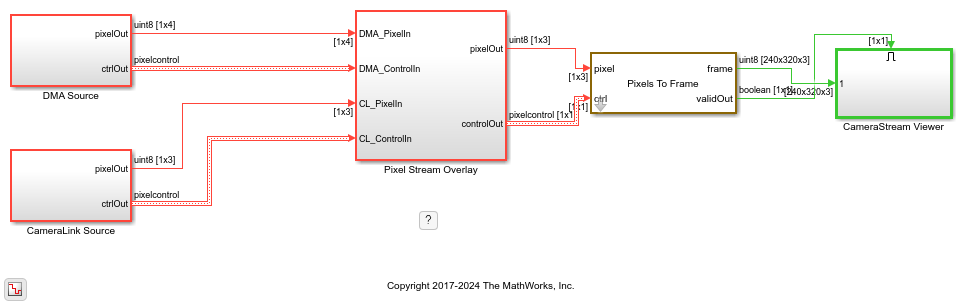

Buffer Bursty Data Using Pixel Stream FIFO Block - MATLAB & Simulink

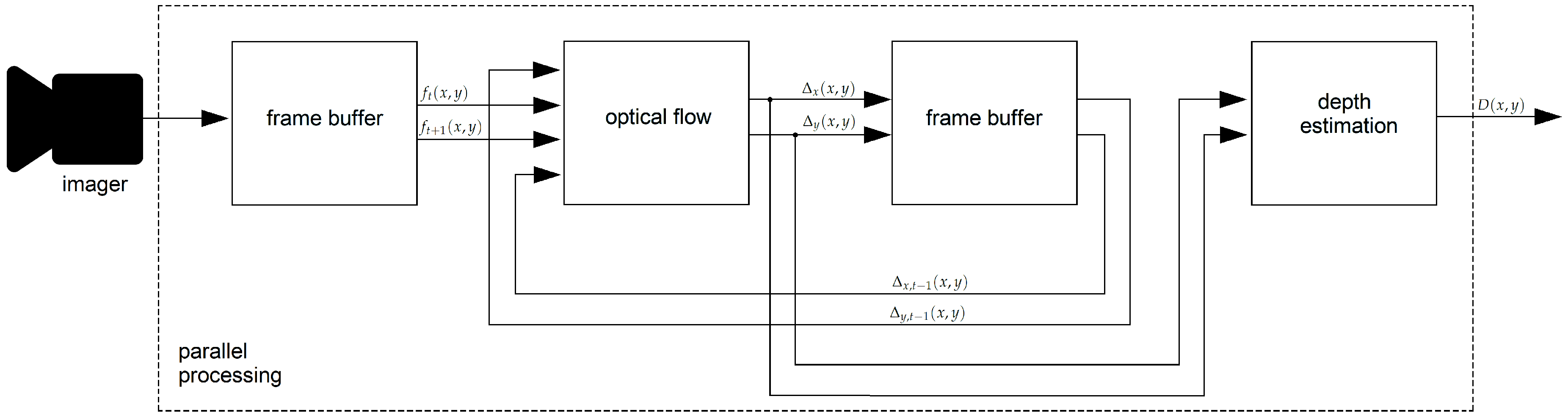

Sensors, Free Full-Text

Real-time Simulink implementation of noise adaptive speech processing pipeline of cochlear implants - ScienceDirect

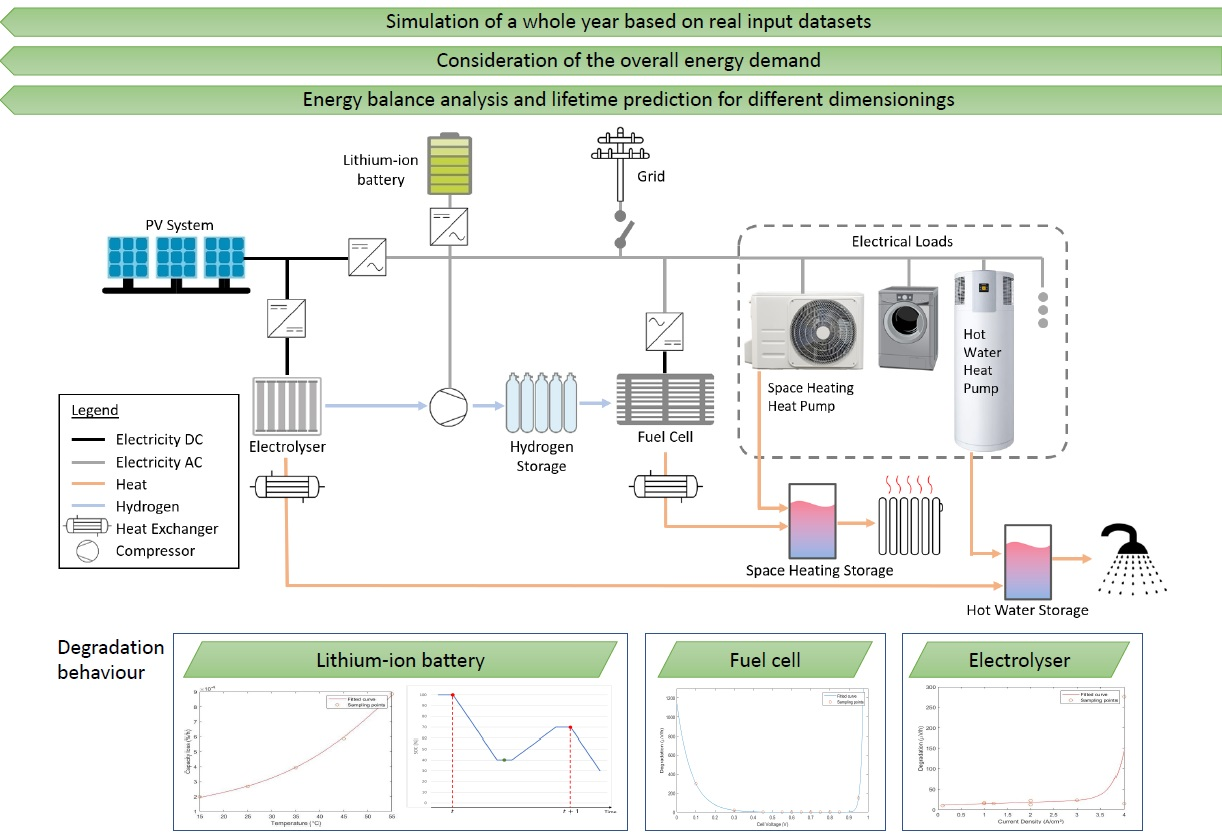

Solar, Free Full-Text

Vertical Video Flipping Using External Memory - MATLAB & Simulink - MathWorks España

Review — Deep Inter Coding with Interpolated Reference Frame for Hierarchical Coding Structure (HEVC Inter), by Sik-Ho Tsang

Low‐latency selective encryption scheme for scalable extension of high‐efficiency video coding - Faragallah - 2022 - Transactions on Emerging Telecommunications Technologies - Wiley Online Library

Create Signals for Frame-Based Processing - MATLAB & Simulink

Efficient FPGA-Based Implementation of Image Segmentation Algorithms for IoT Applications

matlab - Simulink: simulation time buffer issue with scope - Stack Overflow

How to Deploy Frame-Based Models to FPGA/ASIC Using HDL Coder

Figure 4 from Simulation of Triple Buffer Scheme (Comparison with Double Buffering Scheme)

Buffering and Frame-Based Processing - MATLAB & Simulink